台积电2nm工艺步入正轨 苹果AMD英伟达高通预订产能:全面满足市场需求

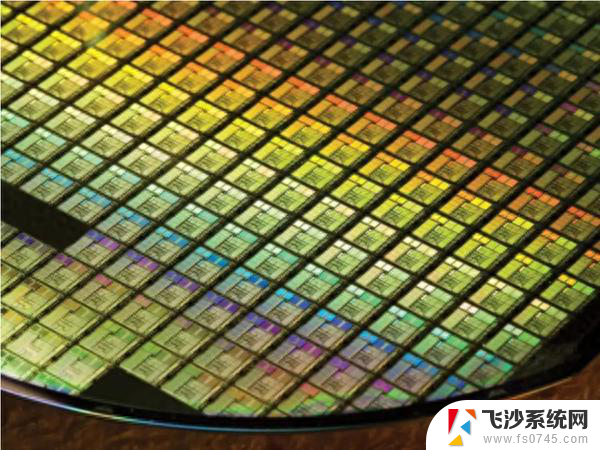

目前,台积电2nm工艺节点在开发过程中表现出色,其缺陷率显著优于3nm和7nm工艺在相同研发阶段的表现。

据报道,该节点芯片的良率现已达到台积电成熟5nm工艺的水平,并预计将于2025年第四季度正式进入大规模量产阶段。

此次技术跃进的关键在于台积电采用了全新的GAAFET(全环绕栅极场效应晶体管)架构。相较于传统的FinFET架构,GAAFET架构中的每个晶体管都采用了被栅极材料完全包裹的nm片结构。这一变革大幅提升了晶体管密度,有效降低了漏电现象,并显著降低了功耗。这是台积电首次在量产芯片中应用GAAFET架构,标志着其在半导体制造技术上的又一次重大突破。

在客户合作方面,AMD成为首批受益者。其下一代代号为“Venice”的EPYC芯片已率先完成流片,预计将成为2nm节点的首发产品。相比之下,苹果的iPhone 18和英特尔的Nova Lake CPU虽也计划采用台积电的2nm技术,但上市时间将稍晚于AMD。

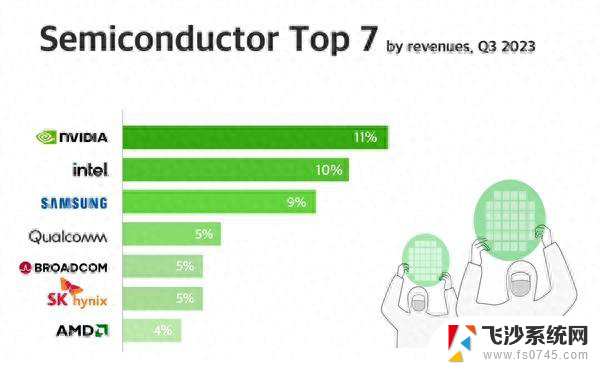

台积电的2nm工艺客户名单堪称豪华,苹果、AMD、英特尔、英伟达、高通、联发科以及博通等芯片设计领域的巨头均已预订产能。其中,英伟达的Rubin GPU最初将采用3nm工艺制造,但未来有望升级至2nm工艺。

台积电董事长魏哲家表示,市场对2nm工艺的需求空前高涨,远超此前3nm工艺引发的抢购热潮。